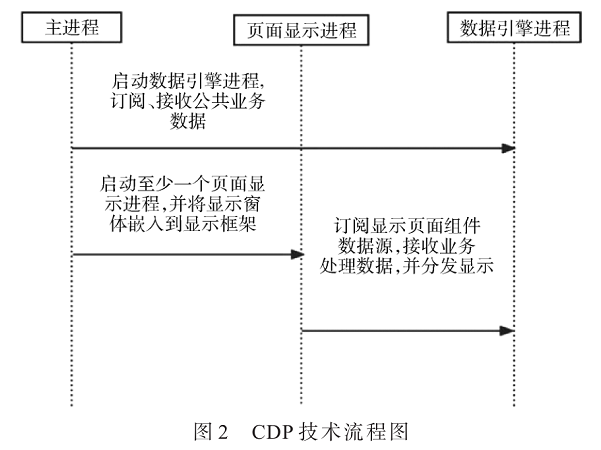

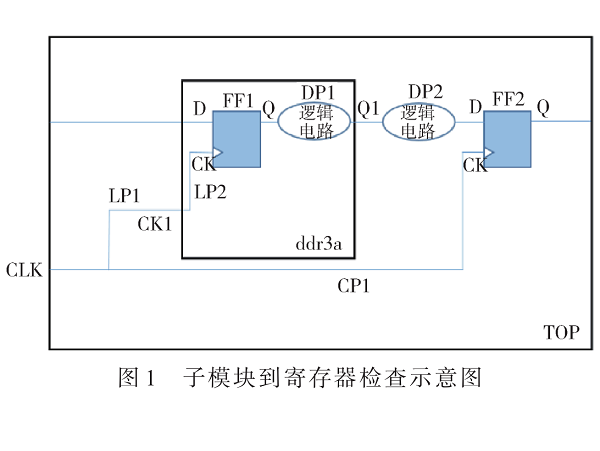

针对态势展示连续性的持续数据保护技术设计[模拟设计][其他]

發(fā)表于:2025/9/16 下午5:14:04

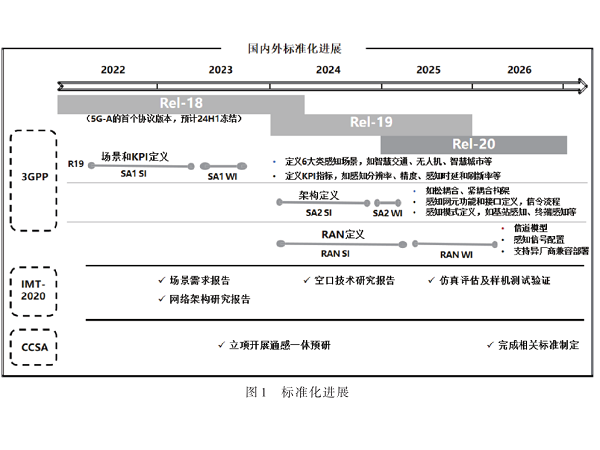

面向5G演进的通信感知一体化技术研究[通信与网络][通信网络]

發(fā)表于:2025/9/16 下午5:03:10

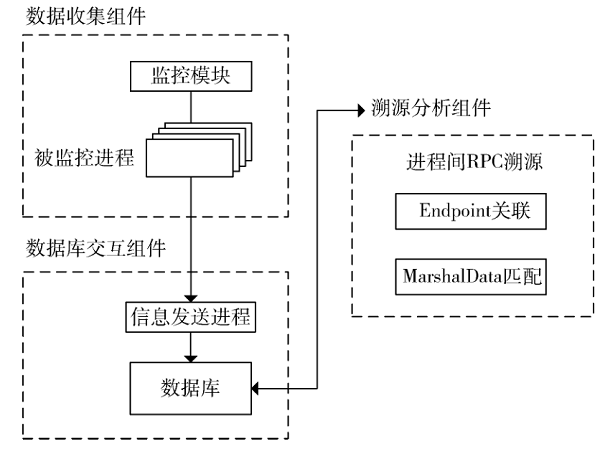

一种基于数据匹配的COM恶意调用溯源研究[通信与网络][信息安全]

發(fā)表于:2025/9/16 下午4:51:57

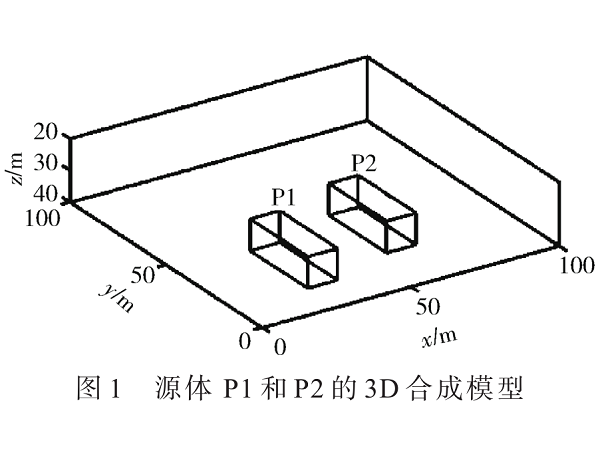

基于无监督机器学习的地质断层识别与深度估算[人工智能][通信网络]

發(fā)表于:2025/9/16 下午4:40:59

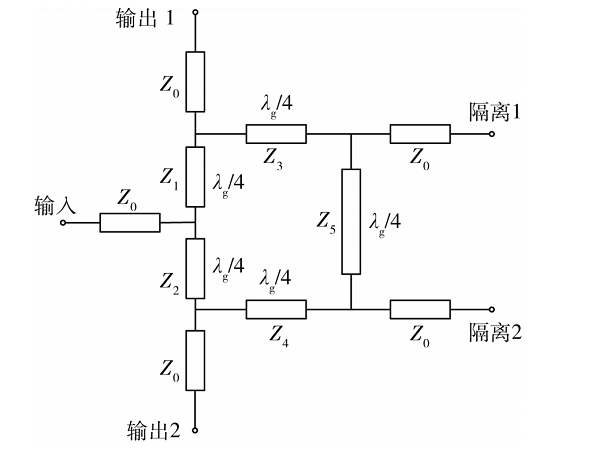

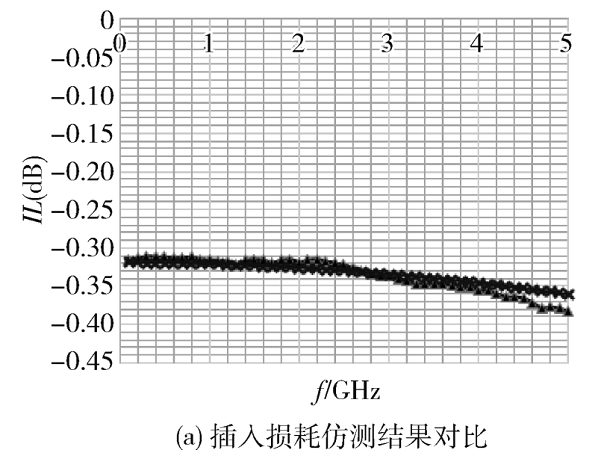

基于SiC IPD技术的小型化大功率Gysel功分器设计[微波|射频][通信网络]

發(fā)表于:2025/9/16 下午4:29:29

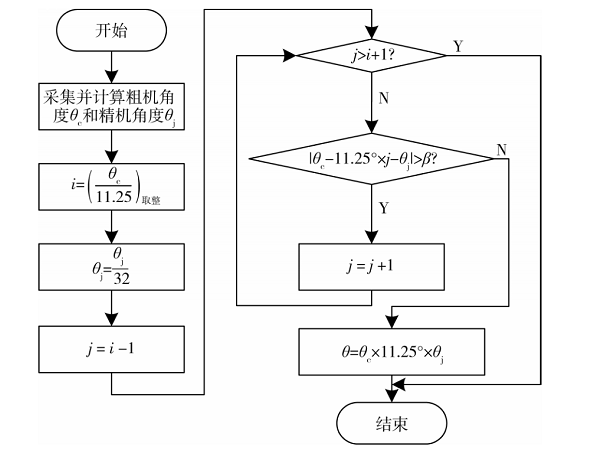

基于CS32F407的双通道旋变解码系统设计[电源技术][汽车电子]

發(fā)表于:2025/9/16 下午3:50:28

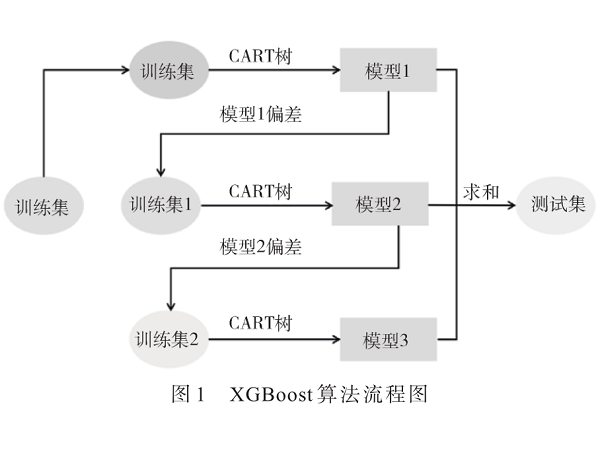

基于数据变换与模型集成的电力需求预测[模拟设计][智能电网]

發(fā)表于:2025/9/16 下午3:25:27

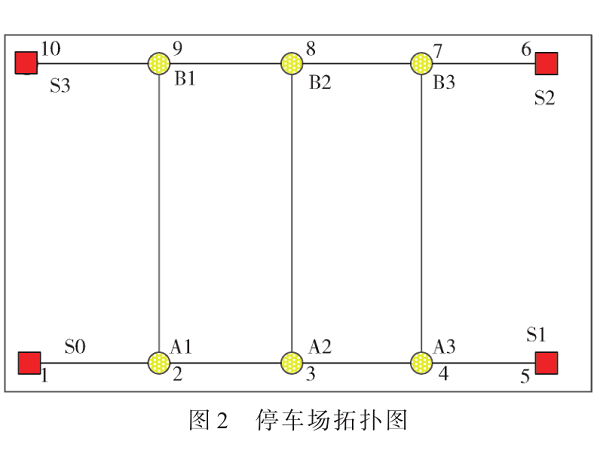

GPS+多线激光雷达的自主路径规划方法[人工智能][汽车电子]

發(fā)表于:2025/9/16 下午3:12:27