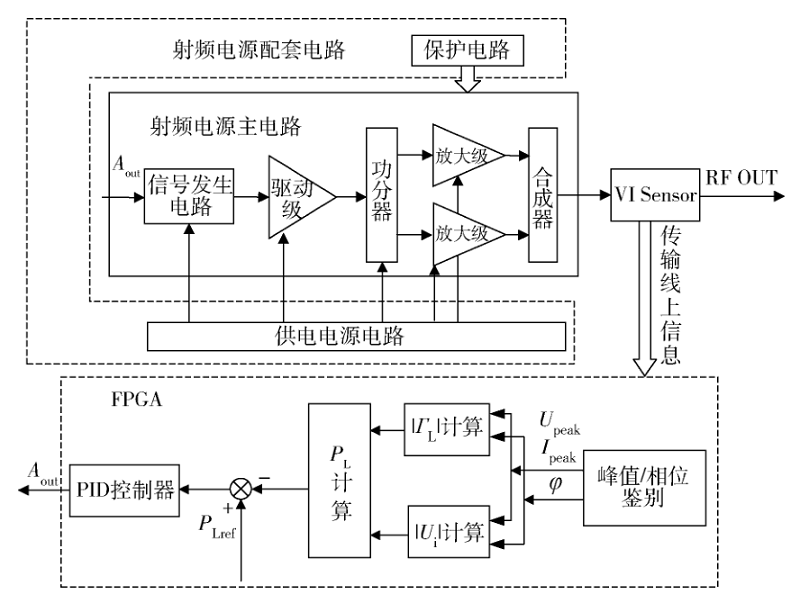

等离子镀膜用射频电源功率计算与控制系统研究[电源技术][工业自动化]

發(fā)表于:2025/10/28 下午4:16:01

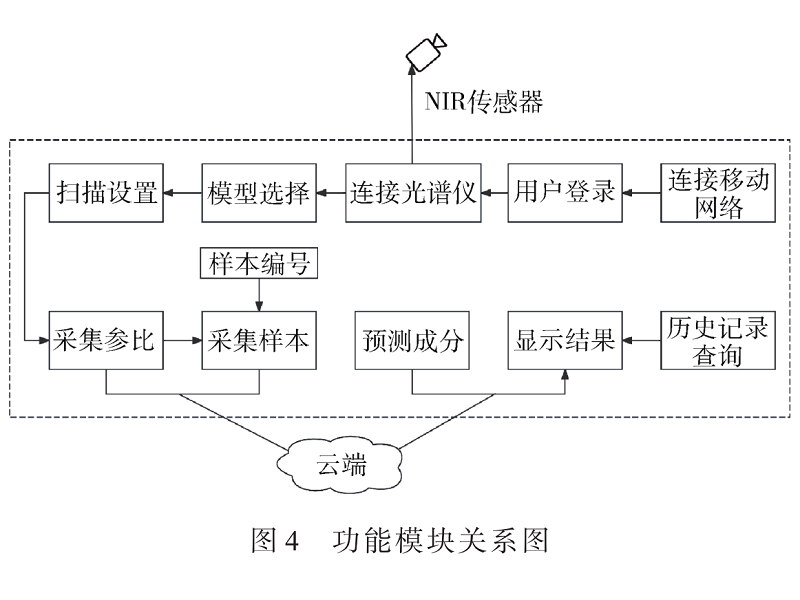

手持式光皮桦种苗叶片生理参数光谱检测设备研制[MEMS|传感技术][其他]

發(fā)表于:2025/10/28 下午4:07:00

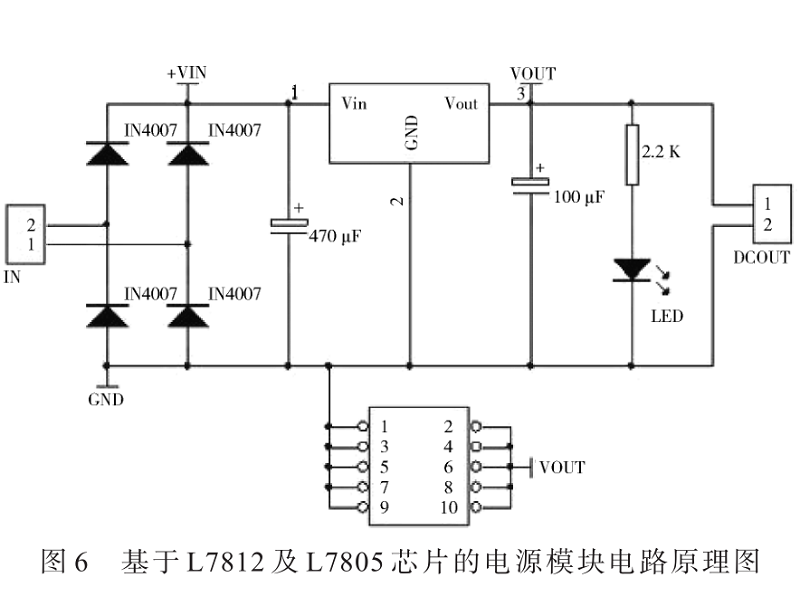

基于PoE技术的多功能可级联全向会议麦克风设计与实现[模拟设计][消费电子]

發(fā)表于:2025/10/28 下午3:58:01

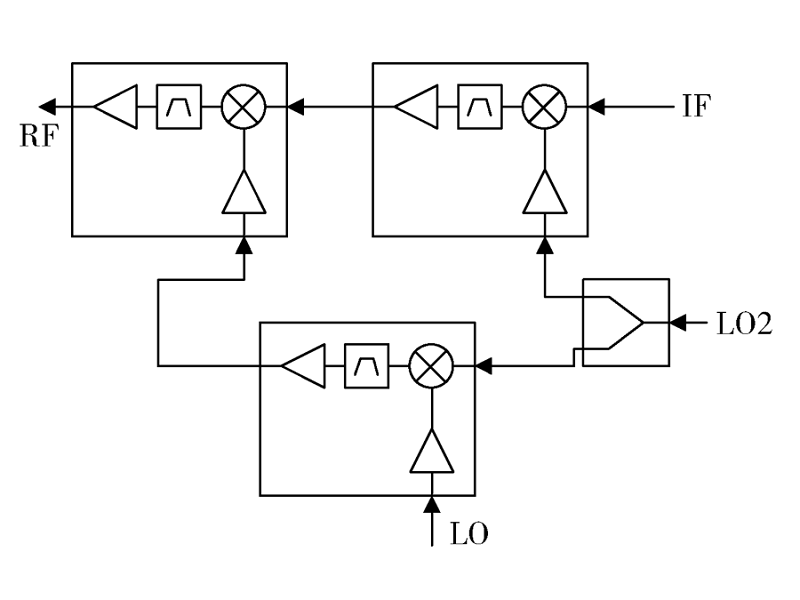

一种能够混合噪声的模拟高频腔的设计及实现[微波|射频][工业自动化]

發(fā)表于:2025/10/28 下午3:39:00

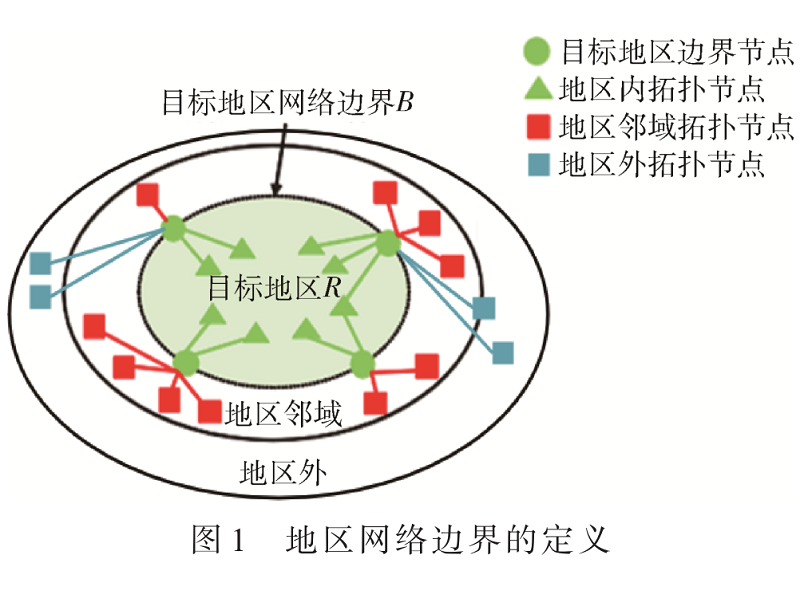

区域网络边界识别技术研究[通信与网络][通信网络]

發(fā)表于:2025/10/28 下午3:30:01

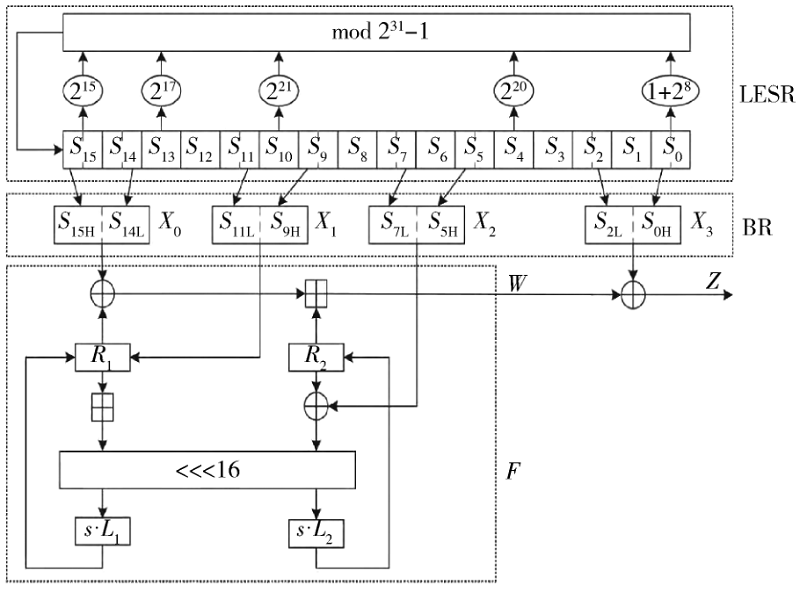

基于FPGA的ZUC算法快速实现研究[可编程逻辑][数据中心]

發(fā)表于:2025/10/28 下午3:21:01

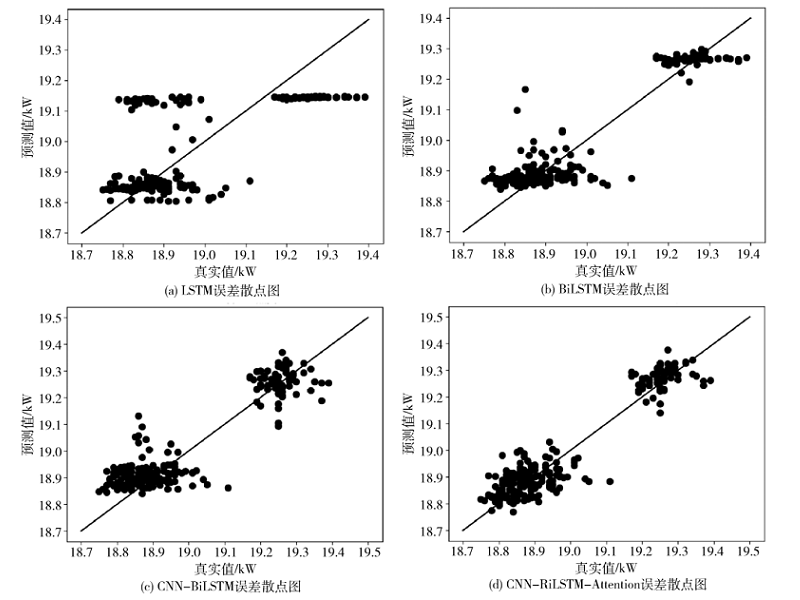

基于CNN-BiLSTM-Attention的工业数据中心IT设备能耗预测模型研究[模拟设计][数据中心]

發(fā)表于:2025/10/28 下午3:10:02

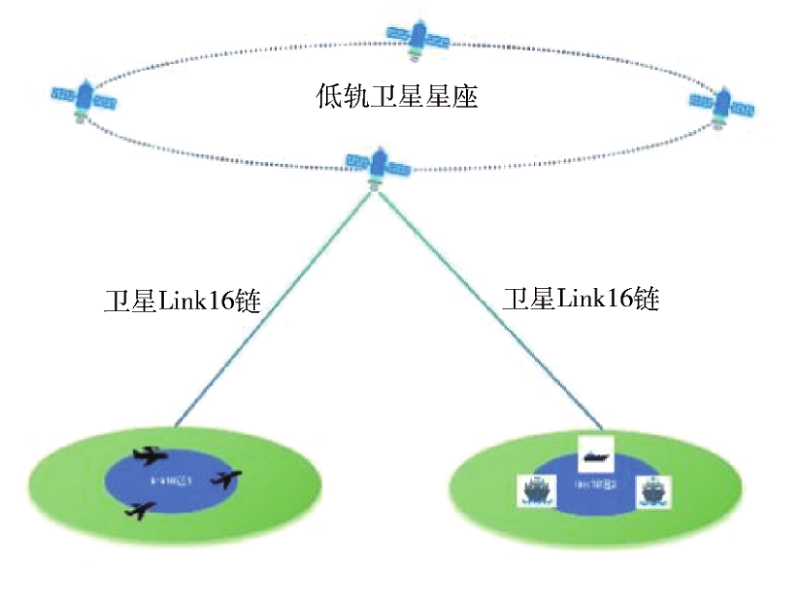

基于位置等效的Link16终端低轨卫星接入设计[通信与网络][航空航天]

發(fā)表于:2025/10/28 下午3:01:57