基于改进LeNet-5的形状类似物体识别方法[人工智能][工业自动化]

發(fā)表于:2020/12/16 下午4:31:44

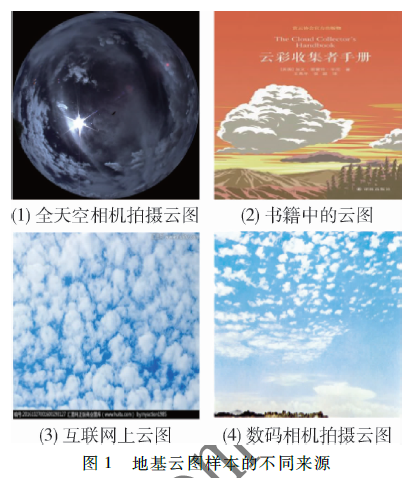

卷积神经网络识别地基云图的数据库建立及处理方法[其他][其他]

發(fā)表于:2020/12/16 下午4:28:00

基于Lucene的中文是非问答系统的设计与实现[模拟设计][其他]

發(fā)表于:2020/12/16 下午4:27:46

基于FTM和CSI的单站目标跟踪研究[通信与网络][通信网络]

發(fā)表于:2020/12/16 下午4:21:39

基于卷积神经网络的织物瑕疵检测方法研究[人工智能][其他]

發(fā)表于:2020/12/16 下午4:13:05

基于改进P-Unet模型的岩屑颗粒识别[人工智能][其他]

發(fā)表于:2020/12/16 下午4:05:58

基于GANs无监督回归三维参数化人脸模型[人工智能][其他]

發(fā)表于:2020/12/16 下午4:00:10

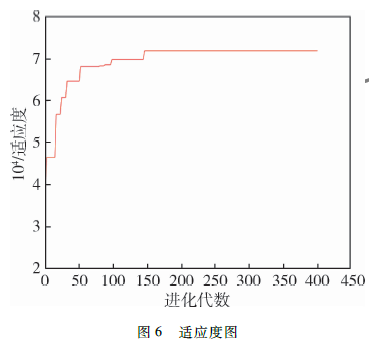

基于二倍体显性机制的透视变换矩阵参数优化[其他][其他]

發(fā)表于:2020/12/16 下午3:58:00