一种新型的采用电流转向电荷泵的快速锁定小数分频锁相环[模拟设计][工业自动化]

發(fā)表于:2020/12/21 上午9:07:00

一种CPT铯原子钟控制系统的设计[模拟设计][工业自动化]

發(fā)表于:2020/12/21 上午9:00:00

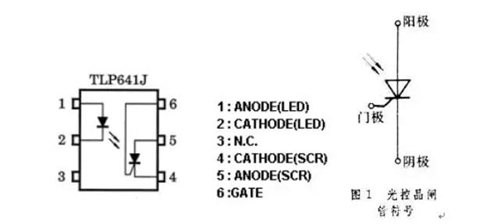

光耦继电器在实际应用中的作用[电子元件][信创产业]

光耦继电器输入输出间互相隔离,电信号传输具有单向性等特点,因而具有良好的电绝缘能力和抗干扰能力。又由于光耦的输入端属于电流型工作的低阻元件,因而具有很强的共模抑制能力。

發(fā)表于:2020/12/20 下午1:30:00

块LBP-TOP稀疏表示表情与车辆检测技术研究[测试测量][汽车电子]

發(fā)表于:2020/12/18 上午10:49:00

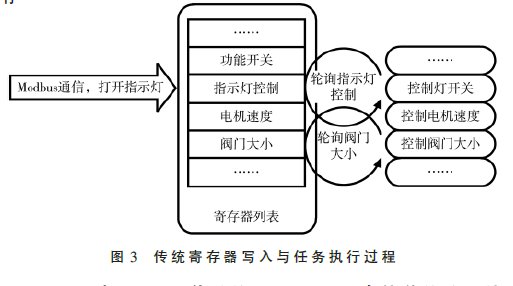

面向超低功耗传感器的Modbus协议研究与实现[MEMS|传感技术][通信网络]

發(fā)表于:2020/12/18 上午9:56:40

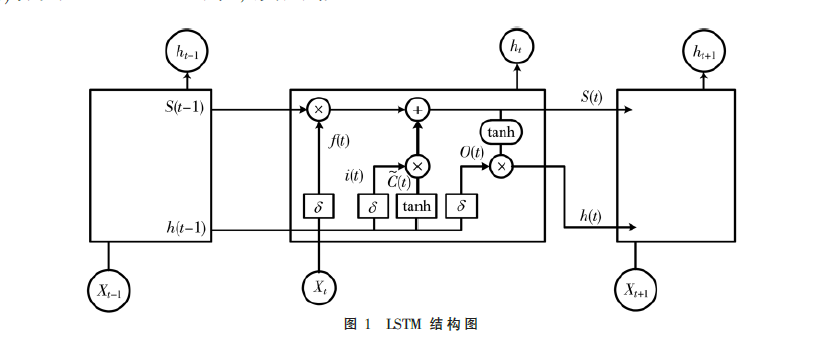

基于LSTM的湿法烟气脱硫浆液pH值建模[模拟设计][工业自动化]

發(fā)表于:2020/12/17 下午5:12:46

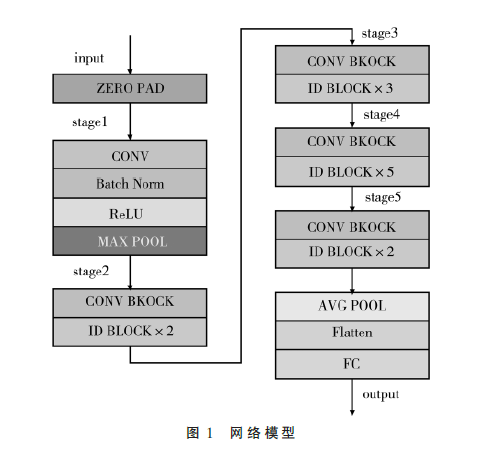

基于深度学习的鱼类识别与检测的算法研究[人工智能][信创产业]

發(fā)表于:2020/12/17 下午5:04:48